## A Report on A Five-Day National Level Workshop on "Hands-On EDA Tools for Semiconductor Manufacturing" Organized by Department of Electronics and Communication Engineering Sponsored by MITS – IEEE, ComSoc (Hybrid Mode) Date:20.01.2025 to 24.01.2025

# Report Submitted by: Dr. G. Naga Jyothi, Dr. G. Naga Swetha and Mr. G Charan Kumar Assistant Professor Department of ECE.

Resource Person Details: Mr Navannetha krishanan Senior Application Engineer Entuple Technologies Bangalore; Dr. Narasimhulu Thoti, Scientific Researcher Microelectronics Research and University of Oulu 90570 Finland; Dr V Bharath Sreenivasulu Assistant Professor Department of Electronics and Manipal University.

Venue: Scaleup Room, MITS Attendees: 15 M. Tech students and 45 Faculty members. Mode of Conduct: Online and Offline Report Received on 30.01.2024.

The Department of Electronics and Communication Engineering (ECE) successfully organized a **Five-Day National Level Workshop on Hands-On EDA Tools for Semiconductor Manufacturing** from **20th January 2025 to 24th January 2025** in the Scaleup Room. The workshop was sponsored by the **MITS IEEE Communication Society** and was aimed at providing participants with practical exposure to Electronic Design Automation (EDA) tools used in semiconductor manufacturing.

#### Workshop Objectives:

The primary objective of this workshop was to enhance participant's knowledge of cutting-edge EDA tools, covering aspects such as simulation, layout design, and process optimization for semiconductor device fabrication. This workshop provided attendees with a comprehensive understanding of the theoretical and practical dimensions of semiconductor manufacturing.

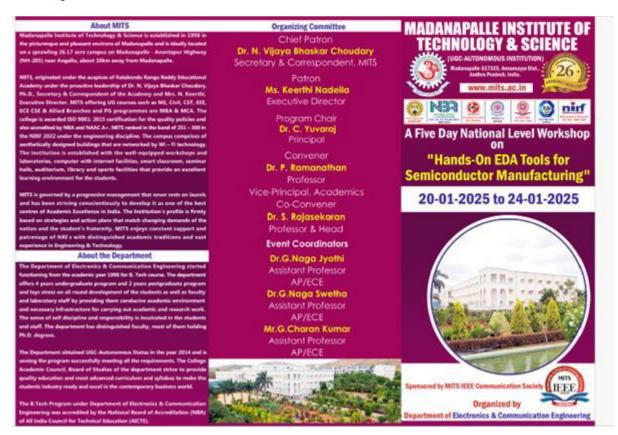

#### **Workshop Brochure:**

| About the Workshop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                | Program Schedule                                                                                                               |                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| in workshop aims to provide participants with practical exposure to<br>extranic Design Automation (EDA) tools, which are pivotal in the<br>rsign, simulation, and manufacturing processes of semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                               | Day       | S. No          | Program Schedule                                                                                                               | Name of the Speaker                                                                                                  |

| esign, simulation, and manufacturing processes of semiconductor<br>prices. The proposed event will cover key topics such as:<br>Circuit simulation and schematic design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | Session 1      | Introduction to semiconductor design using Caden-<br>tool                                                                      | ce.                                                                                                                  |

| Physical layest creation and optimization.<br>Verification techniques including Design Rule Check (DRC) and Layest<br>in. Schematic (LVS).<br>In posiths take doign for manufacturability (DFM).<br>The primary aim of the "Hands-On EDA Tools for Semiconductor<br>Manufacturing" workshop is to provide participants with practical<br>knowledge and skills to effectively utilize Electronic Design Automation<br>(EQA) tools in the design, simulation, and manufacturing of semiconductor<br>derices.<br>To empower participants with hands-on experience in using industry-<br>standard EDA tofbases for verieus stagm of semiconductor design and | Day<br>1  | acsaion 1      | Design of an inverter from schematic to post layout synthesis                                                                  | Mr.Navaneethakrishanan<br>Sr. Application Engineer                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Session 2      | Physical verification, including DRC and LVS of<br>semiconductor designs                                                       | Entuple Technologies                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                | Practical experience in designing, simulating, and verifying semiconductor devices.                                            |                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Day       | Session 3      | Analog circuit design using Cadence Virtuoso                                                                                   | Mr.Navaneethakrishanan<br>Sr. Application Engineer                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2         | Session 4      | Hands on session of analog circuit.                                                                                            | Entuple Technologies                                                                                                 |

| production.<br>Mr.Navanoethakrishanan<br>Secior Appleation Engineer,<br>Estupin Technologies,<br>Bangatore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Day-      | Session-5      | VLSI Emerging devices like FinFET nanowire,<br>nanowheet for CMOS applications                                                 | Dr.V.Bharath<br>Sreenivasulu                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3         | Session-6      | Hands on with Nanohub tool for 2D material based<br>FRTs                                                                       | Dr.V.Bharath<br>Sreenivasulu                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Day-<br>4 | Session-7      | Working with sentaurus/Synopsia TCAD tool for<br>modeling semiconductor devices                                                | Dr.Narasimhulu Thoti                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Session-8      | Device design examples through Sentaurus TCAD.                                                                                 | Dr.Narasimhulu Thoti                                                                                                 |

| Dr.Narasimhulu Thoti<br>Scientific Resarcher<br>Microtochemis Researcher<br>University of Oute, 99570, Finland.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Day<br>5  | Session-9      | Physical Modeling of a device through Sentaurus<br>TCAD &<br>Characterization of semiconductor devices using<br>Sentaurus TCAD | Dr. Managimburks Theat                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Session-<br>10 | Physical Design Flow                                                                                                           | Dr.G.Naga Jyothi                                                                                                     |

| Dr. V. Bharath Sroenivasulu<br>Austrant Professor<br>Department of electronics and Communication<br>Manipal University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (         | MITS           | Cadence                                                                                                                        | For Registration<br>orms.gle/PMTHzvX6YNFMQTUz6<br>PhonePe<br>9849835502-2@yb                                         |

| Dr.G.Naga Jyothi<br>Assistant Professor<br>MITS, Madanayaba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | R<br>Non IEEE  | egistration<br>Member - Rs. 500/-<br>mber - Rs. 400/-                                                                          | For any Query<br>Dr.G.Nogo Swetho<br>Assistant Professor<br>MTS-ECE<br>+91 9649835502<br>Emolt nogowethogtimits oc 3 |

#### **Inauguration Ceremony:**

The workshop was inaugurated on **20th January 2025** in the presence of distinguished guests:

Dr. P. Ramanathan, Vice Principal (Academics) Dr. S. Rajasekaran, Professor & Head, Department of ECE

Dr. Ramanathan Vice Principal Academics his keynote speech, highlighted the significance of EDA tools in advancing semiconductor research and industry applications.

Dr. Rajasekaran HOD ECE delivered the welcome address, emphasizing the importance of hands-on learning in semiconductor technology.

The sessions were conducted by coordinators from the Department of ECE:

- Dr. G. Naga Jyothi, Assistant Professor Department of ECE

- Dr. G. Naga Swetha, Assistant Professor Department of ECE

- Mr. G. Charan Kumar, Assistant Professor Department of ECE

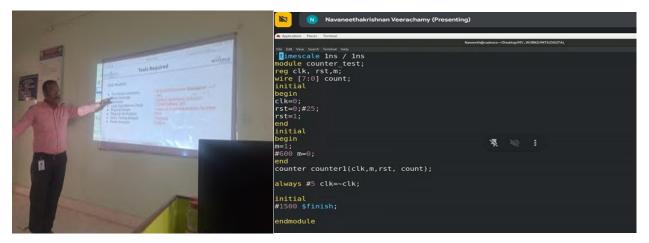

#### Day 1 - 20.01.2025

#### Morning Session - 11: 00 AM to 12:30PM

#### Resource Person: Mr. Navaneetha Krishanan Senior Application Engineer Entuple Technologies Bangalore.

Topic: Introduction to cadence tool using semi-custom design flow & Design of 8 bit counter from RTL to GDSII.

| And and a second se                                                                                                                                                                 | 10:14 👁 👁 <table-cell-columns> •</table-cell-columns> | 腔 閉 네 75% 💼              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------|

|                                                                                                                                                                                                                                                                                | ← 🖬 gzd-pphf-gic                                      | Ø                        |

|                                                                                                                                                                                                                                                                                |                                                       |                          |

| the second s                                                                                                                                                                 |                                                       |                          |

| Applications Places Text Editor                                                                                                                                                                                                                                                |                                                       | The second second second |

| Open - 🖪                                                                                                                                                                                                                                                                       |                                                       |                          |

| <pre>.timescale ins/ins<br/>module counter(clk, m, rst, count);<br/>input clk, m, rst;<br/>output reg [7:0] count;<br/>alway@(posedge clk or negedge rst)<br/>if(ir;<br/>if(ir;)<br/>counter=o;<br/>else if(m)<br/>counter=oint:<br/>countercount:<br/>set<br/>endmodule</pre> | Navaneethakrishnan is pre                             |                          |

|                                                                                                                                                                                                                                                                                | naga i bukke i                                        | Gaur :                   |

|                                                                                                                                                                                                                                                                                | Prav I                                                |                          |

| - i -                                                                                                                                                                                                                                                                          |                                                       |                          |

|                                                                                                                                                                                                                                                                                | III O                                                 |                          |

Mr. Navaneetha krishnan began with an introduction to semiconductor technology, its role in modern electronics, and the importance of EDA tools like Cadence and in the chip design process.

He emphasized the design flow in VLSI, starting from behavioural modelling to physical implementation.

Key challenges in semiconductor design, including power optimization, speed, and area minimization, were discussed.

#### Introduction to the Cadence Tool:

- A brief tutorial on Cadence Virtuoso, the industry's standard platform for IC design, was provided.

- Attendees were guided on how the tool integrates schematic design, simulation, and layout processes into a unified environment.

- The workshop aimed to provide hands-on experience with **Cadence EDA tools** for implementing a **counter** using a **semi-custom VLSI design flow**. The semi-custom methodology enables efficient digital design by leveraging pre-designed standard cells while allowing customization for performance optimization.

#### **Objectives:**

- Understanding the semi-custom design flow for ASIC development.

- Implementing a **counter circuit** using Cadence tools.

- Learning functional verification, synthesis, placement & routing, and timing analysis.

#### **Tools Used:**

The following Cadence tools were utilized:

- Virtuoso Schematic & Layout Design

- Xcelium Functional Simulation

- Genus Logic Synthesis

- Innovus Physical Design (Placement & Routing)

**Design Flow Overview:** The **semi-custom flow** for designing the counter included the following steps: **RTL Design:**

- The counter was coded in Verilog HDL.

- It was designed as a 4-bit synchronous up-counter.

#### **Functional Verification:**

- The Verilog design was simulated using **Xcelium** to verify its functionality.

- Testbenches were written to check count transitions and reset conditions.

#### Synthesis (Using Genus):

- The RTL was synthesized into a **gate-level netlist** using standard cell libraries.

- Synthesis reports (area, timing, power) were analyzed.

#### Placement & Routing (Using Innovus):

- The synthesized netlist was imported into **Innovus**.

- Placement, Clock Tree Synthesis (CTS), and Routing were performed.

- Design Rule Check (DRC) and Layout Versus Schematic (LVS) were run.

#### **Timing & Power Analysis:**

- Static Timing Analysis (STA) was conducted to check setup and hold time violations.

- **Power analysis** was done using **Voltus**.

#### Hands-on Experience:

During the workshop, the following tasks were performed:

- Writing and debugging Verilog code for the counter.

- Simulating the counter in **Xcelium** to verify its behavior.

- Running synthesis in Genus to generate the gate-level netlist.

- Performing floorplanning, placement, and routing using Innovus.

- Checking DRC and LVS for layout correctness.

- Running timing and power analysis for optimization.

#### **Results & Observations:**

- The counter successfully simulated and matched the expected waveform.

- Post-synthesis timing analysis showed minor violations that were optimized.

- Physical design steps (floorplanning, placement, routing) were successfully completed.

- DRC/LVS checks were clean with no errors.

- Power consumption was analyzed, and optimizations were suggested

#### **Practical Applications:**

Mr. Navaneethakrishnan illustrated how these techniques are employed in designing modern ICs used in microprocessors, memory, and communication systems.

Case studies were presented to showcase the scalability of Cadence tools for industrial applications.

#### Day 1 - 20.01.2025

#### Afternoon Session - 02:00 PM to 05:00 PM

# Topic: Physical Verification including DRC and LVS of Semiconductor design and Practical experience in designing, Simulating and Verifying semiconductor devices

#### **Physical Verification: DRC and LVS:**

Physical verification is a critical phase in the semiconductor design lifecycle, ensuring that the fabricated chip will meet design intent and manufacturing constraints. Mr. Navaneethakrishnan's expertise lies in two essential components of physical verification:

#### **Design Rule Check (DRC):**

- **Overview:** DRC is performed to verify that the layout of a semiconductor design adheres to the manufacturing constraints set by the foundry.

- **Practical Experience:** Mr. Navaneethakrishnan has demonstrated excellence in leveraging industry-standard tools such as Cadence Assura, Synopsys IC Validator, and Mentor Graphics Calibre to perform DRC. He has resolved complex rule violations by optimizing layouts and aligning with technology node-specific constraints (e.g., 45nm, 90nm).

#### Layout Versus Schematic (LVS):

- **Overview:** LVS ensures that the physical layout corresponds accurately to the circuit schematic, verifying connectivity and identifying discrepancies.

- **Practical Experience:** He has extensive hands-on experience in running LVS to detect and rectify issues such as shorts, opens, and mismatched device parameters. His ability to debug and resolve these discrepancies ensures robust and error-free designs.

| Applications Places Terminal                                                                                                                                                                                             |                              |                                        |                                                                                | Jan 20 14:53 | 7 | • |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------|--------------------------------------------------------------------------------|--------------|---|---|--|

| Nanoeth@ca                                                                                                                                                                                                               | dence:-/De                   | sktop/MY_V                             | VORKS/MITS/DIGITAL                                                             |              | - | • |  |

| File Edit View Search Terminal Help                                                                                                                                                                                      |                              |                                        |                                                                                |              |   |   |  |

| <pre>create_clock -name clk -period 1 set_clock_transition -rise 0.1 [g set_clock_transition -fall 0.1 [g set_clock_uncertainty 0.01 [get_por set_input_delay -max 0.4 [get_por set_output_delay -max 0.4 [get_por</pre> | et_c<br>et_c<br>orts<br>ts " | locks<br>locks<br>"cll<br>rst"]<br>m"] | "clk"]<br>"clk"]<br>"]<br>-clock [get_clocks "clk"<br>clock [get_clocks "clk"] | 1            |   |   |  |

|                                                                                                                                                                                                                          | ¥                            |                                        | :                                                                              |              |   |   |  |

|                                                                                                                                                                                                                          |                              |                                        |                                                                                |              |   |   |  |

#### Practical Experience in Semiconductor Design and Simulation:

Mr. Navaneethakrishnan has substantial experience across the semiconductor design workflow, including:

Design:

- Skilled in designing CMOS circuits, including analog, digital, and mixed-signal layouts.

- Expertise in schematic capture using tools like Cadence Virtuoso and Mentor Graphics Design Architect.

Simulation:

- Proficient in performing pre- and post-layout simulations to analyse the performance of semiconductor devices.

- Experience with SPICE simulation tools for transient, DC, and AC analyses.

Verification:

- Competent in integrating Physical Verification tools into EDA workflows for seamless DRC and LVS checks.

- Practical involvement in tape-out processes, ensuring that the designs are error-free before fabrication.

Day 2 – 21.01.2025

Morning Session: 10: 00 AM to 01:00 PM Resource Person: Mr. Navaneetha krishanan, Senior Application Engineer, Entuple Technologies, Bangalore. Topic: Analog Circuit Design using cadence virtuoso

#### **Key Topics Covered**

| <b>Introduction to Analog Circuit I</b> | Design:                                                         |

|-----------------------------------------|-----------------------------------------------------------------|

| 0                                       | Basic concepts of analog circuits.                              |

| 0                                       | Importance of analog design in modern electronic systems.       |

| 0                                       | Comparison between analog and digital design methodologies.     |

| <b>Overview of Cadence Virtuoso:</b>    |                                                                 |

| 0                                       | Introduction to the Cadence Virtuoso platform.                  |

| 0                                       | Features and capabilities of Virtuoso in analog circuit design. |

| 0                                       | Interface navigation and basic tool setup.                      |

| Design Workflow:                        |                                                                 |

| 0                                       | Schematic capture and circuit simulation.                       |

| 0                                       | Device modeling and parameter extraction.                       |

| 0                                       | Importance of SPICE models in analog design.                    |

| Simulation and Analysis:                |                                                                 |

| 0                                       | Performing transient, AC, and DC analysis.                      |

| 0                                       | Noise and distortion analysis for analog circuits.              |

| 0                                       | Design optimization using simulation results.                   |

#### • Layout Design and Verification:

- Principles of layout design in analog circuits.

- Parasitic extraction and its impact on circuit performance.

- Design rule checks (DRC) and layout versus schematic (LVS) verification.

#### Hands-On Demonstration:

The session included a hands-on demonstration of designing a simple operational amplifier (Op-Amp) using Cadence Virtuoso. Participants learned how to:

- Create a schematic of the circuit.

- Simulate the circuit for performance evaluation.

- Transition from schematic to layout and ensure design compliance.

#### Day 2 - 21.01.2025 Afternoon Session: 02:00 PM to 05:00 PM **Topic: Hands on Session on Analog Circuit**

#### **Introduction to Analog Circuits:**

- Mr. Navaneethakrishnan explained the foundational concepts of analog circuits, including operational amplifiers, filters, and feedback mechanisms.

- He emphasized the role of analog circuits in modern electronics and their integration with 0 digital systems.

#### **Practical Design Techniques:** 0

- Participants were introduced to practical design methodologies and the significance of component selection in building efficient circuits.

- Common challenges in circuit design were discussed, along with best practices to 0 mitigate these issues.

#### Hands-on Training with Simulation Tools:

- The session included a demonstration of industry-standard tools for circuit simulation, such as Cadence OrCAD and MATLAB.

- Attendees performed real-time simulations of analog circuits under Mr. 0 Navaneethakrishnan's guidance, gaining hands-on experience in analyzing circuit behavior.

#### **Application-Oriented Approach:**

- Real-world applications of analog circuits in areas like signal processing, power 0 management, and communication systems were highlighted.

- Case studies were presented to show how analog circuits are implemented in commercial 0 products.

#### **Q&A and Interaction:**

Mr. Navaneethakrishnan encouraged active participation and addressed queries from 0 students, offering solutions and sharing his industry experience.

#### **Outcomes of the Session:**

- Participants gained practical exposure to analog circuit design and troubleshooting.

- The session bridged theoretical knowledge with practical applications, enhancing the understanding of circuit analysis and simulation.

- Students developed an appreciation for the importance of analog design in various engineering domains. •

#### Feedback:

The session was highly appreciated by attendees, who found it both informative and engaging. Participants highlighted the clarity of Mr. Navaneethakrishnan's explanations and his ability to connect theoretical concepts with practical examples. **Conclusion:**

The hands-on session conducted by Mr. Navaneethakrishnan proved to be an enriching experience for all attendees. It not only deepened their knowledge of analog circuits but also inspired them to explore further applications in the field of electronics. Such industry-focused initiatives significantly contribute to the professional development of students and faculty members alike.

#### **Felicitation of Resource person:**

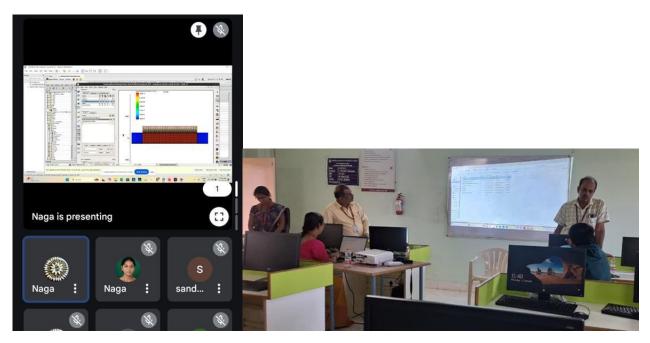

Day 3 – 22.01.2025 Morning Session : 10:00 AM to 01:00 PM Resource Person: Dr Narasimhulu Thoti Scientific Researcher Microelectronics Research and University of Oulu 90570 Finland.

### Topic : Working with Sentaurus/ Synopsis TCAD Tool for modelling semiconductor devices

Dr. Narasimhulu Thoti, a prominent scientific researcher at the Microelectronics Research Unit, University of Oulu, Finland, is recognized for his expertise in modeling and simulation of semiconductor devices. His research primarily involves the application of the Sentaurus Technology Computer-Aided Design (TCAD) tool developed by Synopsys, an advanced platform for simulating the behavior and properties of semiconductor devices.

#### **Overview of Sentaurus/Synopsys TCAD:**

Sentaurus TCAD is a state-of-the-art simulation tool designed to model semiconductor device physics and processes. It integrates physical models to provide insights into the behavior of advanced semiconductor devices under various conditions. The toolset includes modules for:

- Process simulation: Models fabrication steps like ion implantation, diffusion, and annealing.

- Device simulation: Studies electrical, thermal, and optical performance.

- Visualization: Displays 2D/3D device geometries and simulation results.

- Research Focus and Applications

Dr. Thoti's research focuses on utilizing Sentaurus TCAD to address challenges in microelectronics and develop innovative semiconductor solutions. His key areas of interest include:

**Device Optimization and Scaling:** Dr. Thoti employs Sentaurus to explore the effects of scaling down semiconductor devices to nanoscale dimensions. His research aims to optimize transistor performance by studying parameters such as short-channel effects, leakage currents, and device reliability.

- Advanced Material Integration: The integration of novel materials like silicon-germanium (SiGe), gallium nitride (GaN), and two-dimensional materials such as graphene is a significant part of Dr. Thoti's work. Sentaurus helps simulate their behavior in devices, ensuring compatibility and performance enhancements.

- **Energy-Efficient Devices:** With the increasing demand for energy-efficient electronics, Dr. Thoti's work emphasizes low-power device design. Using Sentaurus, he evaluates designs for their energy consumption, thermal stability, and overall performance.

- **Process Variability Analysis:** Variations during fabrication processes can impact device performance. Dr. Thoti uses TCAD simulations to analyze these variations, ensuring robust device design and reduced manufacturing defects.

- **Significance of the Research:** The use of TCAD tools like Sentaurus bridges the gap between theoretical device concepts and practical implementation.

Dr. Thoti's work contributes to:

- Accelerating the design cycle by reducing the need for extensive experimental prototyping.

- Providing a deeper understanding of device physics through simulation.

- Enhancing the performance and reliability of next-generation semiconductor devices

#### Day 3 - 22.01.2025

Afternoon Session : 02:00 PM to 05:00 PM

Resource Person: Dr. Narasimhulu Thoti Scientific Researcher Microelectronics Research and University of Oulu 90570 Finland.

#### Topic : Device Design Examples through Sentaurus TCAD

Device Design Examples through Sentaurus TCAD. Dr. Thoti's research highlights the application of Sentaurus TCAD in the following key areas:

#### 1. MOSFET Design and Optimization:

**Objective:** To improve the performance of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) by exploring alternative materials and geometries.

**Example Work:** Dr. Thoti has designed MOSFETs with high-k gate dielectrics, low-resistance source/drain contacts, and advanced channel architectures like FinFETs and nanowire FETs. Sentaurus TCAD simulations allowed precise analysis of subthreshold slope, drain-induced barrier lowering (DIBL), and mobility enhancement.

#### 2. Power Semiconductor Devices:

**Objective:** Develop power devices, such as IGBTs (Insulated Gate Bipolar Transistors) and SiC MOSFETs, to achieve higher efficiency in power electronics.

**Example Work:** Sentaurus TCAD was employed to simulate electric field distribution, thermal performance, and breakdown voltage in silicon carbide (SiC) and gallium nitride (GaN)-based power devices. His results demonstrate significant improvements in power density and reliability.

#### 3. Solar Cells:

Objective: Enhance the efficiency of photovoltaic devices through material and structural innovation.

**Example Work:** Dr. Thoti used Sentaurus TCAD to design thin-film solar cells with improved light absorption and carrier collection. Simulations focused on tandem solar cells and novel perovskite materials, achieving record efficiency predictions under specific conditions.

#### 4. MEMS Devices:

**Objective:** Integrate Micro-Electro-Mechanical Systems (MEMS) with advanced semiconductors for applications like sensors and actuators.

**Example Work:** His research simulated piezoresistive MEMS sensors using Sentaurus TCAD, optimizing sensitivity, mechanical stability, and energy consumption for IoT applications.

#### Day 4 - 23.01.2025

#### Morning Session: 10:00 AM to 01:00 PM

Resource Person: Dr. Narasimhulu Thoti, Scientific Researcher Microelectronics Research and University of Oulu 90570 Finland.

Topic: Physical Modeling of Device through Sentaurus TCAD & Characterization of Semiconductor devices using Sentaurus TCAD

Research Focus: Physical Modeling and Characterization Using Sentaurus TCAD

#### **1. Overview of Sentaurus TCAD:**

Sentaurus TCAD (Technology Computer-Aided Design) is a powerful simulation framework used for the design and analysis of semiconductor devices. It enables researchers to perform physical modeling, simulate device behavior, and characterize performance before actual fabrication, thereby reducing development costs and time.

#### Key features of Sentaurus TCAD include:

- Support for multidimensional simulations (1D, 2D, and 3D).

- Advanced physical models for charge transport, heat dissipation, and quantum effects.

- Capabilities to simulate novel materials and devices, such as compound semiconductors, heterostructures, and nanoscale devices.

#### 2. Physical Modeling of Semiconductor Devices:

Dr. Thoti's research leverages Sentaurus TCAD to develop highly accurate physical models of various semiconductor devices. The key steps in this process include:

- **Device Structure Design:** Using advanced geometry editors and mesh generators in Sentaurus, Dr. Thoti constructs detailed 2D and 3D device structures.

- Material Parameterization: Incorporating material properties, such as bandgap, mobility, and recombination coefficients, for materials like Si, Ge, GaN, and other III-V compounds.

- **Transport Mechanism Modeling:** Simulating carrier dynamics (drift-diffusion, hydrodynamic transport, and quantum tunneling) and studying the effects of these mechanisms on device performance.

- **Process Simulations:** Employing process simulation tools within Sentaurus TCAD to model ion implantation, diffusion, oxidation, and other fabrication steps.

#### 3. Characterization of Semiconductor Devices:

Using Sentaurus TCAD, Dr. Thoti performs comprehensive characterization of semiconductor devices, including:

- **Electrical Characterization:** Simulating current-voltage (I-V) characteristics, capacitance-voltage (C-V) profiles, and threshold voltage shifts to assess device behaviour under various biasing conditions.

- **Thermal Analysis:** Modeling self-heating effects and heat dissipation to evaluate device reliability under high-power operation.

- **Optical Analysis:** Investigating photonic interactions in optoelectronic devices, such as solar cells and photodetectors.

- **Reliability Testing:** Analysing degradation mechanisms, including hot carrier injection (HCI), bias temperature instability (BTI), and time-dependent dielectric breakdown (TDDB).

#### Day 4 – 23.01.2025

#### Afternoon Session: 02:00 PM to 05:00 PM

Resource Person: Dr Narasimhulu Thoti Scientific Researcher Microelectronics Research and University of Oulu 90570 Finland.

### **Topic : Physical Design Flow**

Physical Design Flow refers to the transformation of a circuit's logical representation into its physical layout, which can then be fabricated on a silicon wafer. This process is integral to the development of modern integrated circuits (ICs) and involves various stages, including:

- **Partitioning and Floorplanning:** Breaking down the design into smaller blocks and arranging them within a defined chip area while optimizing for performance, power, and area.

- **Placement:** Assigning precise locations to each cell or module in the design, ensuring minimum delay and power consumption.

- Clock Tree Synthesis (CTS): Designing a clock distribution network to ensure synchronized operation across the chip.

- **Routing:** Establishing connections between components using metal layers, adhering to design rules to minimize resistance, capacitance, and interference.

- **Design Rule Checking (DRC):** Verifying that the layout adheres to the fabrication process's geometric and electrical constraints.

- Timing Analysis: Ensuring the design meets timing constraints to avoid delays or functional errors.

#### Felicitation of Resource Person:

## Day 5 : 24.01.2025

Morning Session: 10:00 AM to 01:00 PM Resource Person: Dr. V. Bharath Sreenivasulu, Assistant Professor, Department of Electronics & Communication Engineering, Manipal University.

#### Topic : VLSI Emerging Devices like FinFET nanowire, nanosheet for CMOS Applications

As CMOS technology progresses towards nano-dimensions, conventional planar transistors are facing significant challenges due to short-channel effects, leakage currents, and limitations in scaling. The demand for energy-efficient, high-performance, and highly scalable devices has driven innovations in VLSI (Very-Large-Scale Integration) technology. Emerging transistor architectures like FinFETs, nanowires, and nanosheets are becoming the frontrunners in overcoming these limitations and enabling the next generation of CMOS applications.

#### **Emerging Devices in VLSI:**

#### 1. FinFET (Fin Field Effect Transistor)

FinFETs are one of the most widely adopted solutions to the scaling limitations of planar MOSFETs. They feature a threedimensional structure with a "fin"-like channel that rises above the substrate.

#### **Key Characteristics:**

- Enhanced electrostatic control of the gate over the channel.

- Reduction in leakage current due to better gate control.

- High drive current and switching speeds.

#### **Applications:**

FinFETs are extensively used in modern processors and memory technologies due to their energy efficiency and scalability to sub-10nm nodes.

#### 2. Nanowire Transistors

Nanowires take transistor scaling a step further by utilizing cylindrical or rectangular channel structures that offer better gate control compared to FinFETs.

#### **Advantages:**

- Full gate-surrounding architecture for superior electrostatic control.

- High on/off current ratios.

- Improved performance for ultra-scaled dimensions.

#### **Applications:**

Nanowires are suitable for low-power, high-density CMOS applications, making them a potential candidate for future systemon-chip (SoC) technologies.

#### 3. Nanosheet Transistors:

Nanosheets are an evolution of nanowire transistors and are designed to address the limitations in current flow associated with nanowires. These devices stack flat, wide sheets as channels, offering enhanced drive currents while retaining excellent electrostatic control.

#### **Key Features:**

- Improved drive current compared to nanowires.

- Compatibility with advanced manufacturing techniques like extreme ultraviolet (EUV) lithography.

#### **Applications:**

- Nanosheets are considered the next step in CMOS transistor scaling and are expected to dominate technology nodes below 3nm.

- Advantages of Emerging VLSI Devices for CMOS Applications

- Better Short-Channel Control: Devices like FinFETs, nanowires, and nanosheets mitigate short-channel effects, allowing further scaling of transistors.

- **Energy Efficiency:** These structures reduce leakage currents and enhance energy efficiency, crucial for batteryoperated and IoT devices.

- Scalability: Their three-dimensional designs offer greater scalability, making them viable for sub-10nm nodes and beyond.

- Challenges and Future Directions: While these emerging devices address many issues associated with traditional CMOS technology, challenges remain

- Fabrication Complexity: Advanced manufacturing techniques such as EUV lithography are required, increasing production costs.

- Material Limitations: The integration of novel materials like high-k dielectrics and low-resistance contacts is crucial for further performance improvements.

• **Reliability Concerns:** As device dimensions shrink, maintaining reliability and minimizing variability become critical concerns.

#### Day 5 - 24.01.2025

#### Afternoon Session - 02:00 PM to 05:00 PM

Resource Person: Dr. V. Bharath Sreenivasulu, Assistant Professor, Department of Electronic & Communication Engineering, Manipal University

Topic : Hands on with Nanohub tool for 2D material based FETS

Nanohub is an online platform providing a comprehensive suite of simulation tools and resources for research and education in nanotechnology. It allows users to access various simulation models for different nanomaterials and devices, offering capabilities in modeling, characterization, and performance evaluation. It has become an essential tool for researchers and educators working with nanoscale materials and devices, providing a seamless environment for simulation without the need for extensive hardware setups.

#### Session Highlights:

#### **Introduction to 2D Materials and FETs**

Dr. Sreenivasulu began by introducing the concept of 2D materials, which are materials that consist of a single or few layers of atoms. Their remarkable electronic properties, such as high carrier mobility, flexibility, and strong quantum confinement, make them ideal candidates for the development of future FETs. He explained the advantages of using 2D materials over conventional silicon, highlighting the potential for faster, more efficient, and miniaturized devices.

#### The Role of Nanohub in FET Design

The session focused on the use of Nanohub tools for simulating and analyzing 2D material-based FETs. Dr. Sreenivasulu demonstrated how to access and use the tools on Nanohub, showing the basic steps to set up simulations for 2D FETs. He explained the importance of simulating material properties such as band structure, charge transport, and device behavior under different operating conditions. Participants were introduced to specific tools such as Quantum ATK, NanoTCAD, and Sentaurus for detailed device simulations.

#### Hands-on Session:

Dr. Sreenivasulu guided the participants through a series of practical exercises using Nanohub's tools. They began by selecting appropriate 2D materials, such as MoS2 or graphene, and inputting parameters like material thickness, gate dielectric properties, and bias conditions. The participants then conducted simulations to analyze key characteristics such as the subthreshold slope, on-off current ratio, and threshold voltage of the FETs. These simulations helped the participants understand the impact of material selection and device design on the overall performance of the FET.

#### **Challenges in 2D Material-Based FETs:**

During the session, Dr. Sreenivasulu discussed some of the challenges associated with 2D material-based FETs, such as issues with contact resistance, scalability, and material stability. He emphasized the need for advanced simulation techniques to predict and mitigate these issues before moving to experimental fabrication. The role of Nanohub tools in optimizing device design and identifying potential failure points before physical testing was also highlighted.

#### **Future Prospects and Applications:**

Dr. Sreenivasulu concluded the session by discussing the future applications of 2D material-based FETs, such as in flexible electronics, low-power devices, and high-performance computing. He stressed that understanding the intricacies of 2D material-based device behavior through simulations is crucial for accelerating the development of these novel technologies.

#### **Felicitation of Resource Person:**

#### **Newspaper Clips:**

#### ఆధునిక సాంకేతికతపై అవగాహన

అంగట్ల (కురబలతోట), న్యూస్టుడే : ఆధునిక సాంకేరిక తపై అవగాహన పెంచుకోవాలని బెంగళూరుకు చెందిన సీని యర్ అఫ్రికేషన్ ఇంజినీర్ నవసీతకృష్ణన్ తెలిపారు. మిద్చీ కళా శాల ఆవరణలో కార్యశాలను సోమవారం వైస్ ట్రిగ్సెపల్ దాక్టర్ రామనాథన్ ప్రారంపించారు. కార్యక్రమంలో విభాగాథపతి దాక్టర్ రాజశేఖరన్, కోఅర్షినేటర్ దాక్టర్ నాగజ్యాతి, డాక్టర్ నాగ శ్వేత, చరజ్ తదితరులు పాల్గొన్నారు.

Date : 21/01/2025 EditionName : ANDHRA PRADESH( ANNAMAYYA ) PageNo :

### నూతన ఆలోచనలతో ముందుకు సాగాలి

టరబలకోట, జనవరి 20(ఆంధ జ్యోరి): విద్యార్శులు, అధ్యావకులు నూతన ఆలోచనలతో ముందుకు సా గాలని రిసోర్శువర్గన్ నవసీత్ కృష్ణన్ పేర్కొన్నారు. సోమవారం మండలం లోని మిట్స్ ఇంజనీరింగ్ కళాళాలలో సెమీకండెక్టర్ తయారీకి ఈడీఏ సాధ నాల ఆదరణాత్మక ఉపయోగంపై వర్క్ షాప్ నిర్వహించారు. ఈ నందర్భంగా

సమావేశంలో మాట్రాడుతున్న రిసోధ్యపర్సన్ నవసీత్ కృష్ణన్

ఆయన మాట్లాడుతూ పరిశ్రమలు ఆకడ మిశ్చపై దూరం తగ్గించదానికి పరిశోధనలు పేపట్టి మంచి ఫరితాలను సాదించాలని కోచారు. ప్రస్తుతం సాఫ్ట్రేష్ రంగంతో పోల్చితే ఈసీఈ రంగంలో మెరుగైన ఉద్యోగాన కాశాలు ఉన్నాయన్నారు. ప్రధాని మోడీ ష్యాబ్ సిదీన మంజూరు దేశారని, దీనిలో ఎంజెడెడ్ వీఎల్ఎన్ఐఏడిఎ జిక్నాలజీలు ఎంతగానో డోపాద పడుతాయని వాటిపై పట్టు సాదించాలని నూచించారు. ఈ కార్యకమంలో విభాగాధిపతి రాజశేఖరన్, నాగజ్వేతి, నాగశ్వేత, చరన్ తదితరులు పాల్చొన్నారు.

మిట్డ్ కణాశాలలో సెమీ కండక్టర్ తయాలికి ఈడిది.. సాధనాల ఆచరణాత్మక ఉపయోగం అను అంశంపై.

బదు రోజుల వర్మ్ షాప్ ప్రారంభం.. ముభ్యఅతిభిగా హాజరైన నవనీత కృష్ణన్..

వైస్ ప్రిన్నిపాల్ డాక్రర్ రామనాధన్ వెల్లడి.

మదనపల్లి (నిఘా సూర్య) మదనపల్లె ఇన్స్టేట్యూట్ ఆఫ్ టెక్నాలజీ, సైన్స్ (మిట్స్ ) కళాశాల నందు సెమీకందర్లర్ తయారీకి ఈడిఏ సాధనాల

అచరణాత్మక ఉపయోగం అను అంశం పై ఐదు రోజుల వర్యేషాప్ ను సోమవారం ప్రారంభించారు. వర్య్షోఫ్ ను పరిష్ఠాత్మకమైన జఈఈఈ వారు ఆద్వర్యంలో నిర్వహించినట్ల కళాశాల వైస్ బ్రీన్సపాల్ దాక్టర్ రామనాథన్ అన్నారు. ఈ కార్యకమానికి ముఖ్య అరిధిగా నవనీతకృష్ణవొ, సీనియర్ అప్లికేషన్ ఇంజనీర్, డిజైన్ ఈ డి ఏ సపోర్ట్, ఎంటుపుల్ టెక్నాలజీస్ -ສັດກັນສໍສາດັນ పాల్గొ న్నారు. కార్యక్రమంలో అయన మాట్లాడుతూ పరిశమలకు.అకదమిక్ కి మధం అంతరంను తగించదానికి, పరి(శమల

సమస్యల పై రీసెన్స్ ద్వార పరిష్కరించి సరైన ఆలోచనలతో ముందుకెళ్ళి, మంచి ఫలితాలను రాజట్టు ఇటువంటి టూల్స్ ఎంతగానో ధోహద పదతాయని తెలిపారు. ఇటువంటి అద్వాన్స్ డ్ టూల్స్ కొనుగోలు i పీజీ స్పూడెంట్స్ పరిశోధనలు అతిత్వరగా పూర్తి చేయుటకు మంచి అవకాతం ఉందన్నారు. ప్రస ్రార్యాల్స్ సాఫ్ట్రీక్ ఉద్యోగాలతో పోలిస్తే తనీత విధాగము విద్యార్థులకు మెరుగైన అవకాశాలు స్నాయని చెప్పారు. ముఖ్యంగా వి.ఎల్.ఎస్.జ, ఎంబెబెడ్ సిస్టమ్స్ పై పెండుగా ఉన్నాయన్నారు. ప్రస్తు మన ప్రధానమంత్రి నరేంద్ర మోడీ ఫ్యాబ్ సిటీస్ మంజారు చేశారని,అవి నిర్మాణ దశలో ఉన్నాయ శెలిపారు.శ్వరలో అవి అందుబాటులోకి వస్తాయన్నారు. వి.ఎల్.ఎస్.ఐ ఈ డి ఏ. టూల్స్ పై మనం అవగాన పెంచుకొని, పరిశోధనలు చేయాలని సూచించారు. ప్రస్తుతం ఏ ఫ్యాటికేషన్ కి అయినా మనం ఇంశ కంపెనీ పై ఆధారపడి ఉన్నామని సూచించారు.మన ఇండియాలో కొత్త టెక్నాలజీకి సరైన అవగాహన లే! ఇటు వంటి వర్యేషాప్లకు హాజరవడం వళ్ల ఇందస్ట్రీలో జరుగుతున్న పరిశోదనలను విద్యార్యులు రెలుసుక కర్యర అధువాతన సాధనాల తో నూకవ పరిలోచినలు చేయాలన్నారు. కార్యకమంలో విభాగాధిపతి దా రాజశేఖరన్, కో ఆర్టిపేటర్ దాక్టర్ నాగ జ్యారి, దాక్టర్ నాగశ్వేత, చరన్ తదితరులు పాల్గొన్నారు.

ఐ.ఈ.ఈ.ఈ ఆధ్వర్యంలో

మిట్ఫ్ లో వర్మ్షేషాప్ ప్రారంభం

## ఐఈఈఈ ఆధ్మర్యంలా మిట్మ్ కణాశాల వర్మ్షేషాప్ ప్రారంభం

మదనపల్లె,జనవరి 20(కురుక్రేతం ప్రతినిధి) :అంగళ్లు సమీపంలోని మదనపల్లె ఇన్స్టిట్యూట్ ఆఫ్ టెక్నాలజీ అంద్ సైన్స్ (మిట్స్ కళాశాల) నందు సెమీకందక్టర్ తయారీకి (ఈడిఏ) సాధనాల ఆచరణాత్మక ఉపయోగం అనే అంశంపై ఐదురోజుల వర్మ్షేషాప్ ను సోమవారం ప్రారంభించారు. వర్క్రిషాప్ ను ప్రతిష్ఠాత్మకమైన (బతుతుతు) వారు అద్వర్యంలో నిర్వహించినట్లు కళాశాల వైస్ (పిన్సిపాల్ దాక్టర్ రామనాథన్ అన్నారు.ఈ కార్యక్రమానికి ముఖ్య అతిథిగా నవనీత కృష్ణన్, సీనియర్ అప్లికేషన్ ఇంజనీర్,డిజైన్ మరియు ఈదీఏ సపోర్ట్, ఎంటుపుల్ టెక్నాలజీస్ – బెంగుళూరు పాల్గొన్నారు. ఈ కార్యక్రమంలో ఆయన మాట్లాదుతూ పరి(శమలకు మరియు అకడమిక్స్.కి మధ్యంతరా న్ని తగించదానికి మరియు పరిశ్రమల సమస్యలపై రీసెర్స్ ద్వార హాజరవడం వళ్ల ఇండస్ట్రీలో జరుగుతున్న పరిశోధనలనుహా పరిష్కరించి సరైన అలోచనలతో ముందుకెళ్లి,మంచి ఫలితాలను రాబట్ట్ర్ విద్యార్థులు తెలుసుకొని తద్వారా అధునాతన సాధనాలతో నూతన దానికి ఇటువంటి టూల్స్ ఎంతగానో ధోహదపదతాయని పేర్కొన్నారు. పరిశోధనలు చేయాలన్నారు. ఈ కార్యక్రమంలో విభాగాధిపతి దాక్టర్ ఇటువంది అద్వాన్స్ ద్ టూల్స్ కౌనుగోలు చేసి పీజీ స్టూడెంట్స్ రాజశేఖరన్,కో-ఆర్డినేటర్ దాక్టర్ నాగజ్యేతి,దాక్టర్ నాగశ్వేత,చరన్ పరిశోధనలు అతిత్వరగా పూర్తి చేయుటకు మంచి అవకాశం ఉ తదితరులు పాల్గొన్నారు.

ందన్నారు.(ప్రస్తుత పోటీ ప్రపంచంలో సాఫ్ట్వేర్ ఉద్యోగాలతో పోలిస్తే ఈసీఈ విభాగము విద్యార్థులకు మెరుగైన అవకాశాలు ఉ న్నాయని,ముఖ్యంగా వి.ఎల్.ఎస్.ఐ మరియు ఎంజెదెడ్ సిస్టమ్స్ పై మెండుగా ఉన్నాయన్నారు.ప్రస్తుతం మన ప్రధానమంత్రి నరేంద్ర మోదీ ఫ్యాబ్ సిటీస్ మంజూరు చేశారని,అవన్ని నిర్మాణ దశలో ఉన్నాయని త్వరలో అవి అందుబాటులోకి వస్తాయన్నారు. (వి.ఎల్.ఎస్.ఐ ఈడిఎ) టూల్స్ పై మనం అవగాహన పెంచుకొని,పరిశోధనలు చేయాలనీ ఆయన అన్నారు. ప్రస్తుతం ఏ ఫ్యాబికేషన్ కి అయినా మనం (ఇంటెల్) కంపెనీపై అధారవడి ఉన్నామన్నారు.మన ఇండియాలో కొత్త టెక్నాలజీకి సరైన అవగాహన లేదని ఇటు వంటి వర్కషాప్లకు

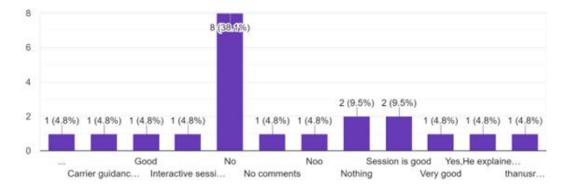

#### **Feedback from Students:**

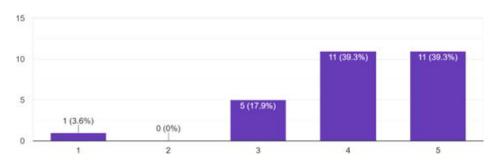

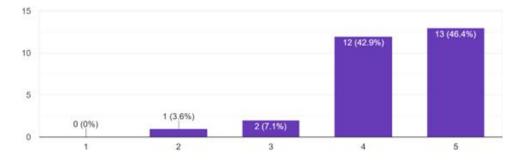

1. The interactive session was scheduled at a suitable time

2. The interaction was useful and resource person explanation. 28 responses

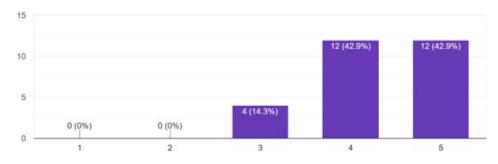

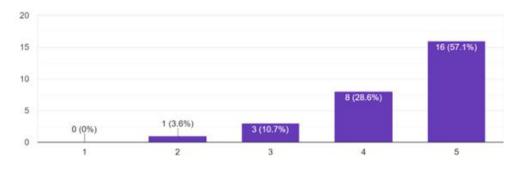

3. The information in the interaction was presented in a clear and organized manner. 28 responses

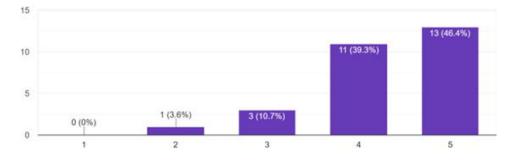

4. The presenter responded to questions an informative, appropriate and satisfactory manner. 28 responses

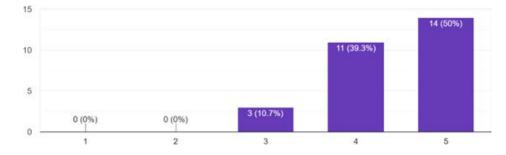

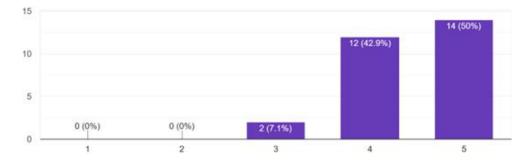

5. your impression of facilities provided by the institute for interaction. 28 responses

6. Overall, the session was informative and valuable. 28 responses

7. In what ways could this interaction have been improved to better suit your needs? 28 responses

#### 8. Any Other Comments

21 responses